Miglioramenti architetturali dell’IGP in Sandy Bridge

Le CPU Sandy Bridge vedono per la prima volta l’introduzione della IGP nello stesso die della CPU vera e propria.

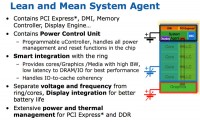

Specificatamente, notiamo che la GPU integrata in Sandy Bridge è totalmente parificata a tutto il resto, in quanto essa dispone dello stesso accesso alla cache L3 che hanno i core della CPU, grazie ad un ring bus che interconnette contemporaneamente la Cache L3, l’IGP, i Core ed il Memory Controller. Questa novità è particolarmente importante poiché consente di ottimizzare i tempi di acceso della IGP alla memoria senza penalizzare quella della CPU. Occorre però specificare che la GPU, dal punto di vista dell’alimentazione, è completamente indipendente dal resto. Il consumo e le frequenze sono infatti gestiti dinamicamente, mantenendo i limiti del TDP prestabiliti e fissati a 95W per entrambe le due CPU analizzate oggi. La gestione dinamica del Turbo Boost della CPU e della GPU in relazione al TDP complessivo rientra nelle novità introdotte con l’architettura Sandy Bridge.

La gestione indipendente dei voltaggi e delle frequenze di CPU, IGP e System Agent è un altro punto chiave per la gestione dinamica dei consumi e delle prestazioni in modalità turbo e in overclock delle CPU Sandy Bridge.

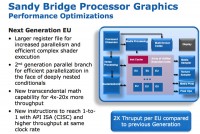

Altro particolare di grossa importanza, sono le unità ‘shaders/cores/execution’ che Intel ora chiama EU, ognuna di queste unità riesce a gestire le istruzioni dal sistema multi-threading, ovviamente queste sono perfettamente compatibili con le istruzioni API DirectX 10.1. Relativamente alle EU Intel ha introdotto importanti miglioramenti che, rispetto alla precedente generazioni di EU integrate nelle CPU Clarkdale, promettono incrementi prestazionali fino al 100%. I principali miglioramenti riguardano l’adozione di un registro più ampio per l’esecuzione di un maggior numero di thread in parallelo, un’unità di riordino delle istruzioni più efficiente, un’unità per i calcoli trascendentali da 4 volte fino a 20 volte più efficiente e un nuovo set di istruzioni in grado di completare i requisiti ISA per le architetture CISC. In particolare ora ogni thread ha a disposizione un numero prefissato di 120 registri, mentre in precedenza il numero medio di registri per thread era di soli 64. In precedenza veniva adottata una politica di allocazione dinamica secondo le esigenze, strategia che portava a un risparmio di area di silicio ma sicuramente non consentiva le stesse performance di registri dedicati.

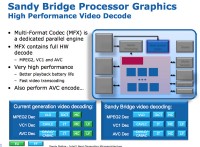

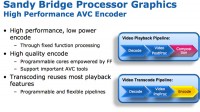

Integrato nella GPU per aumentare le prestazioni di codifica multimediale, Intel, ha provveduto ad inserire il Media Engine. Per funzionare correttamente, questo sistema di codifica necessita di software predisposto a questo tipo di sistema. Il Media Engine è dotato di unità dedicate sia per il decoding sia per l’encoding.

Troviamo accelerazione hardware dedicata per la decodifica di flussi MPEG-2, VC1 (utilizzato nei blu-ray) e AVC (ultimo standard di codifica dell’MPEG-4). Anche la codifica e la transcodifica dei medesimi flussi ha subito un boost sostanziale, portando la IGP di Sandy Bridge ai livelli delle schede video discrete. Intel ha racchiuso queste feature sotto il nome di Quick Sync, presente su tutta la gamma di IGP Intel HD 3000 e HD 2000.